Guia inovador para os flip-flops JK: analisando tabelas, mecanismos e aplicações estratégicas

Este artigo explora a arquitetura, operação e diversas aplicações do FLIP-FLOP JK, a partir de sua estrutura básica e relações de entrada e saída, por meio de mecânica operacional detalhada, até suas implementações estratégicas em sistemas digitais complexos.O discurso se estende a distinguir entre as variantes acionadas por arestas e acionadas por nível, analisando seus respectivos utilitários em ambientes síncronos e assíncronos.Catálogo

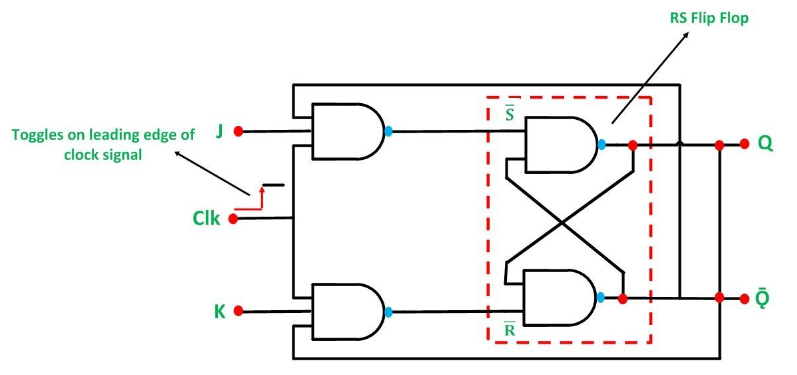

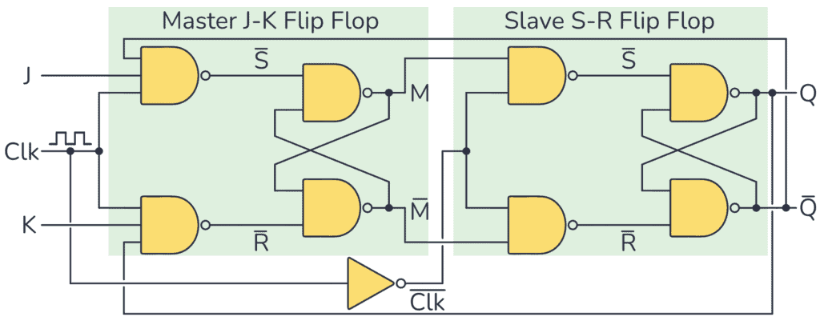

Figura 1: JK FLIP-FLOP

Noções básicas de jk flip-flop

O JK FLIP-FLOP é um componente básico em eletrônicos digitais, projetado para armazenar um único pedaço de informação.Ele se baseia no flip-flop SR mais simples, adicionando feedback, o que ajuda a evitar erros conhecidos como "condições de corrida", onde a saída se torna instável.

Este flip-flop possui duas entradas principais, j (set) e k (redefinir) e duas saídas: q e seu complemento, q '.Essas saídas refletem continuamente o estado atual e seu oposto, permitindo que o circuito ajuste e responda às alterações de entrada em tempo real.

O FLIP-FLOP JK opera de maneiras específicas com base nos valores de entrada:

• Quando J e K são 0: O flip-flop mantém seu estado atual.Nenhuma mudança ocorre.

• Quando J e K são 1: O flip-flop alterna seu estado.Se q é 0, ele se torna 1;Se q for 1, ele alterna para 0. Essa ação de alternância é um recurso-chave que distingue o flip-flop JK de designs mais simples.

• Quando J é 1 e K é 0: O flip-flop define seu estado, tornando Q igual a 1.

• Quando J é 0 e K é 1: O flip-flop é redefinido, tornando Q igual a 0.

Operação do jk flip-flop

O FLIP-FLOP JK desempenha um papel fundamental nos circuitos digitais, gerenciando a memória e o tempo através de uma resposta coordenada a sinais de entrada e pulsos de relógio.Sua operação depende muito do tempo das entradas J e K em relação ao sinal do relógio, que determina como a saída dos estados (q e q̅) muda.Essa sincronização garante que o flip-flop se comporte previsivelmente em várias aplicações de circuito.O flip-flop conta com NAND ou nem portões para gerenciar essas mudanças de estado.

Segurando o estado atual- Quando as entradas J e K são baixas (0), o flip-flop mantém seu estado atual.Os portões lógicos efetivamente "bloqueiam" as saídas, garantindo que o estado anterior (alto ou baixo) seja mantido.Essa função de retenção é séria em aplicativos em que os dados devem permanecer estáveis até que uma alteração específica seja obrigatória.

Definindo a saída alta (estado definido) -Quando o pulso do relógio ocorre e J é alto (1) enquanto K permanece baixo (0), os portões lógicos se ajustam para definir o flip-flop.Isso leva a saída Q para um estado alto (1).Isso é útil em situações em que o circuito precisa acionar uma saída alta, por exemplo, ativando um dispositivo ou armazenando um "1" na memória.

Limpando a saída baixa (estado de redefinição) - Se J for baixo (0) e K for alto (1) no momento de um pulso de relógio, o flip-flop transita para um estado de redefinição, forçando Q a diminuir (0).Essa ação de redefinição é frequentemente usada em circuitos que precisam de um estado inadimplente ou limpo após a conclusão de uma operação, como a limpeza de dados da memória.

Alternando a saída - O recurso exclusivo do flip-flop surge quando J e K são altos (1).Quando o pulso do relógio chega, o flip-flop alterna, alternando a saída de seu estado atual para o oposto.Se q é alto, fica baixo e, se q é baixo, ficará alto.Essa função de alternância é insistente em aplicativos como contadores ou dispositivos que precisam alternar entre os estados automaticamente.

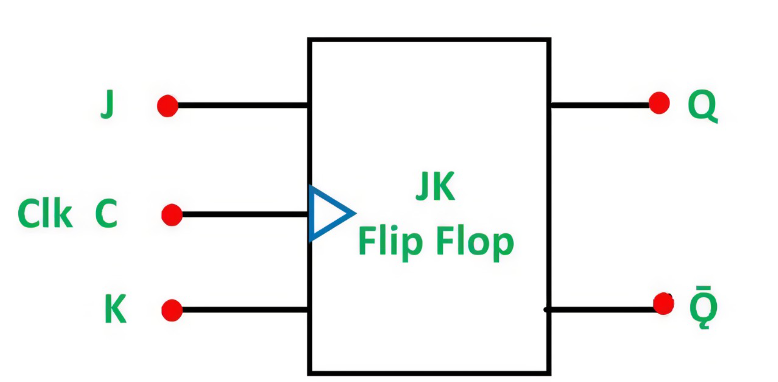

Figura 2: JK Flip-Flop Truth Table

Análise da tabela de verdade JK flip-flop

A tabela de verdade do FLIP-FLOP JK é uma ferramenta-chave para visualizar como ela reage a diferentes sinais de entrada em sincronia com pulsos de relógio.Esta tabela ajuda a projetar e solucionar os circuitos digitais, mostrando como as saídas do flip-flop mudam com base em várias condições de entrada.

• J e K BOW (J = 0, K = 0): Quando ambas as entradas são 0, o flip-flop mantém seu estado atual.Se q é alto ou baixo, permanece inalterado.Isso é digno de nota para os circuitos onde é procurada retenção estável de dados, como elementos na memória, onde a preservação do estado atual é adequada até que uma alteração específica seja acionada.

• J alto, k baixo (j = 1, k = 0): Quando J é 1 e K é 0, o flip-flop define a saída Q a High (1).Essa condição de configuração é útil em aplicativos que exigem um gatilho preciso para ativar uma operação, como ativar um dispositivo ou iniciar uma sequência em um circuito lógico.

• J baixo, k alto (j = 0, k = 1): Com J em 0 e K em 1, o flip-flop é redefinido, tornando Q Low (0).Essa função de redefinição é grave em sistemas que precisam retornar a um estado padrão, como ao limpar dados ou inicializar um processo.

• J e K High (J = 1, K = 1): Quando ambas as entradas são altas, o flip-flop alterna seu estado.Se q estiver alto, fica baixo e, se q é baixo, muda para o alto.Esse comportamento de alternância é substancial para dispositivos que precisam alternar entre estados, como em divisores de frequência ou contadores.

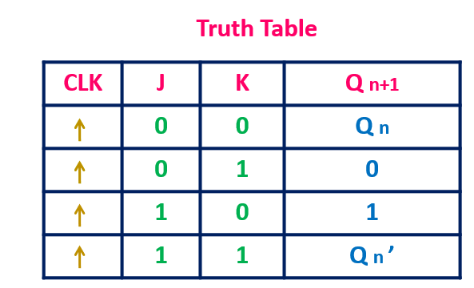

Figura 3: JK trava

Insights sobre a operação de trava JK e usa

A trava JK opera de maneira semelhante ao jk flip-flop, mas sem a necessidade de um sinal de relógio.Em vez de esperar por uma borda do relógio, a trava JK responde continuamente para inserir mudanças, tornando-a "sensível ao nível".Isso significa que, desde que as entradas (J e K) sejam estáveis, a saída mudará em tempo real, oferecendo feedback imediato com base nas condições de entrada.

Ao contrário do Flip-flop JK acionado por borda, que atualiza sua saída somente quando o sinal do relógio muda (de baixo para alto ou vice-versa), a trava JK ajusta sua saída instantaneamente à medida que as entradas mudam.Essa resposta constante e em tempo real é valiosa em cenários em que a ação imediata é desejada sem o atraso causado pela sincronização do relógio.

Filtros de ruído: Nos circuitos digitais que precisam filtrar rapidamente o ruído indesejado, a reação instantânea da JK Latch às alterações de entrada é influente.Como não espera por um pulso de relógio, ele pode ajustar a saída assim que o ruído for detectado, impedindo atrasos na correção do sinal.

Elementos de memória simples: A trava JK pode servir como uma unidade de memória básica em sistemas que não exigem controle complexo e com relógio.Como a trava mantém a saída estável, desde que as entradas não mudem, ele efetivamente mantém o estado atual, o que é útil para os circuitos que precisam reter informações sem a sobrecarga das operações clocked.

Figura 4: Análise do diagrama de tempo para o jk flip-flop

Analisando o diagrama de tempo do JK Flip-flops

Um diagrama de tempo do FLIP-FLOP JK fornece uma quebra visual de como a saída responde a diferentes entradas, sincronizadas com as transições de pulso do relógio.Este diagrama mostra a relação entre o sinal do relógio (CLK) e as entradas (J e K) e como elas influenciam coletivamente as saídas (q e q ').Ajuda a mapear o comportamento do flip-flop em estados seqüenciais, facilitando a compreensão de sua operação.

Em primeiro lugar, o diagrama destaques que as saídas são atualizadas apenas nas bordas nascentes ou quentes do relógio.Esse recurso, conhecido como acionamento de arestas, é dominante para a operação do JK Flip-Flop.Isso mostra que, mesmo que as entradas J e K mudem, a saída permanecerá inalterada até que a borda do relógio ocorra, garantindo transições previsíveis e estáveis.

Então, como o diagrama mapeia as variações de entradas J e K, ele visualmente demonstra como cada combinação de entrada afeta a saída. Por exemplo, quando J e K são baixos (0), a saída mantém seu estado atual.Quando J é alto e K é baixo, a saída é definida.Essa representação visual clara ajuda os usuários a entender como o flip-flop reage a diferentes combinações de entrada em tempo real.

Finalmente, O diagrama de tempo mostra claramente as transições entre diferentes estados de saída, sejam segurando, definindo, redefinindo ou alternando.Cada mudança de estado está ligada diretamente às condições de entrada e à borda do relógio, mostrando uma relação de causa e efeito que é focal para projetar e solucionar circuitos de solução.

Aplicações versáteis de flip-flops JK

Os flip-flops JK são componentes principais em uma ampla gama de sistemas digitais, conhecidos por sua flexibilidade e confiabilidade.Sua capacidade de lidar com operações lógicas complexas os torna necessários em vários aplicativos importantes, incluindo:

Figura 5: armazenamento de memória

Os flip-flops JK são comumente usados para armazenar bits de dados individuais, tornando-os elementos fundamentais em matrizes e registros de memória.Cada flip-flop é um bit, garantindo armazenamento de dados confiável, o que é benéfico no design de sistemas de memória maiores.

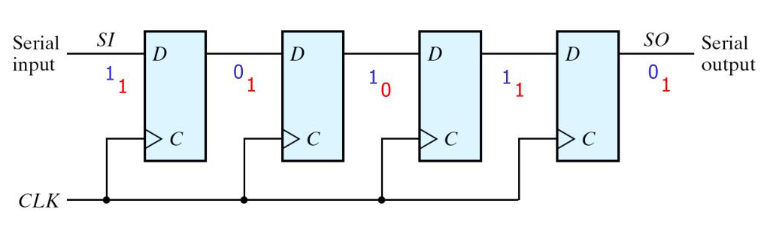

Figura 6: contadores e registros de turno

Os flip-flops JK são dinâmicos nas operações de sequenciamento.Eles são amplamente utilizados em contadores para contar eventos ou pulsos e nos registros de turno para converter dados seriais em formatos paralelos.Isso os torna úteis no gerenciamento e manipulação de dados em diferentes estágios de um processo, como nos sistemas de comunicação.

Figura 7: Divisão de Frequência

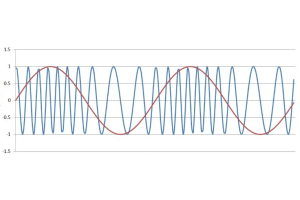

No processamento de sinal, os flip-flops JK são frequentemente usados para divisão de frequência.Ao alternar seu estado com cada pulso do relógio, eles dividem a frequência do sinal de entrada, criando um sinal de relógio mais lento e gerenciável.Isso é digno de nota em aplicativos como gerenciamento de sinal de relógio, onde o controle de tempo é desejado.

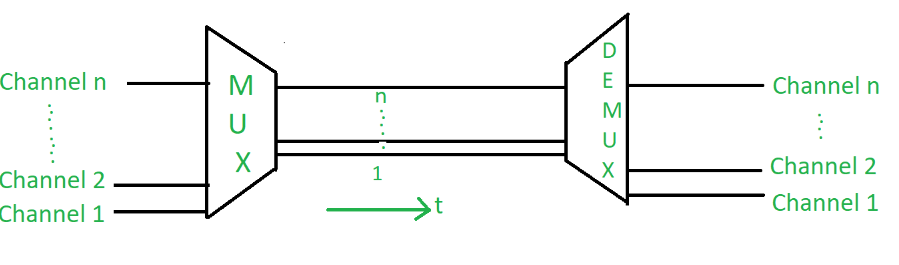

Figura 8: Sincronização

Os flip-flops JK ajudam a sincronizar vários processos digitais, garantindo que diferentes partes de um sistema operem juntas de maneira coordenada.Eles garantem que vários componentes respondam corretamente aos sinais cronometrados, mantendo todo o sistema em sincronia.

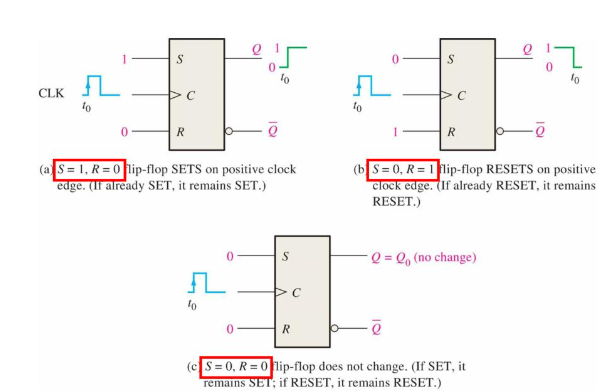

Figura 9: JK FLIP-FLOP: acionado por arestas e acionado por nível

Diferentes tipos de flip-flops JK

Os flip-flops JK estão disponíveis em dois tipos principais: acionados por arestas e acionados por nível, cada um projetado para diferentes requisitos operacionais.

Flip-flops JK acionado por borda: Altere seu estado apenas em pontos específicos - quando o sinal do relógio transita de baixa para alta (borda ascendente) ou alta para baixa (borda de queda).Essa característica os torna ideais para sistemas em que o tempo preciso é insistente.Como as mudanças de estado ocorrem exatamente na borda do relógio, esses flip-flops garantem que todas as atualizações ocorram sincronizadas com o pulso do relógio.Esse comportamento previsível é dinâmico em ambientes bem controlados, como relógios digitais, registros e circuitos mais seqüenciais.Aqui, o tempo de cada alteração é grave para manter a estabilidade do sistema e garantir que as operações sejam sincronizadas.

Flip-flops JK acionado por nível: Operar de maneira diferente, reagindo ao sinal de entrada, desde que o sinal do relógio esteja em um nível específico - seja alto ou baixo.Eles não esperam por uma transição específica do relógio.Em vez disso, desde que a entrada atenda às condições necessárias, o flip-flop mudará os estados.Esse comportamento faz com que os flip-flops desencadeados por nível mais adequados para sistemas assíncronos, onde as entradas podem não se alinhar com um pulso regular de relógio.Eles fornecem flexibilidade em sistemas em que os insumos são imprevisíveis ou chegam a intervalos irregulares, como em determinadas tarefas de processamento de sinal ou sistemas de monitoramento que devem reagir imediatamente à alteração de entradas.

Prós e contras do jk flip-flop

Os flip-flops JK oferecem vários benefícios, mas também vêm com algumas compensações que precisam ser cuidadosamente pesadas ao projetar sistemas digitais.

|

Prós |

|

|

Versatilidade |

Os flip-flops JK são altamente flexíveis e podem

ser usado em vários circuitos digitais, como armazenamento de memória, contadores e

Sistemas de controle.Eles podem alternar, definir ou redefinir com base em diferentes entradas

condições, tornando -as adequadas para uma ampla gama de aplicações que

requer controle preciso sobre transições de estado. |

|

Mecanismo de autocorreção |

Um dos recursos de destaque de JK

Os flip-flops são o seu loop de feedback embutido, o que ajuda a corrigir lógicos

estados dinamicamente.Esta autocorreção garante que o circuito permaneça

estável durante a operação, mesmo quando as entradas mudam rapidamente. |

|

Mitigação da condição de corrida |

Ao contrário dos flip-flops mais simples, JK flip-flops

são projetados para evitar condições de raça - situações em que a saída se torna

instável devido a sinais de entrada conflitantes.Essa capacidade de manter

saída consistente, mesmo em alterações rápidas e seqüenciais de entrada, melhora o

confiabilidade do circuito. |

|

Contras |

|

|

Design complexo |

Os chinelos JK são mais complicados do que

Flip-flops básicos.Seu design requer portões lógicos e entrada adicionais

monitoramento, o que pode tornar o circuito mais difícil de projetar e

Solução de problemas, especialmente em sistemas onde a simplicidade é preferida. |

|

Atraso de propagação |

O bloqueio interno usado para gerenciar o estado

As transições introduzem um atraso na forma como os sinais podem ser processados.Em

Aplicações de alta velocidade, esse atraso pode afetar o tempo geral e diminuir a velocidade

o desempenho do circuito. |

|

Maior consumo de energia |

Devido à sua complexidade e à necessidade de

Monitorar constantemente as condições de entrada, os flip-flops JK consomem mais energia

comparado a flip-flops mais simples.Em sistemas maiores ou sensíveis à energia

Aplicações, essa maior demanda de energia pode se tornar uma desvantagem |

Figura 10: Flip-flop JK-escravo mestre

Decodificando o flip-flop JK-escravo mestre

O FLIP-FLOP JK-Slave Master-Slave foi projetado para resolver a condição de corrida encontrada nos flip-flops JK padrão usando um processo de duas etapas para gerenciar entradas e saídas com mais eficiência.

O primeiro estágio, chamado de estágio mestre, captura os valores de entrada quando o sinal do relógio atinge uma borda específica, subindo ou descendo.Nesse ponto, os dados de entrada estão bloqueados, o que significa que ainda mais mudanças nas entradas não afetam o estado capturado até o próximo ciclo do relógio.Este estágio garante que o flip-flop registre a entrada correta sem ser influenciada por quaisquer alterações subsequentes durante o mesmo ciclo de relógio.

Depois que o estágio mestre é concluído, o estágio de escravo entra em jogo.Este estágio atualiza a saída com base nos dados capturados pelo estágio mestre, mas apenas na próxima borda do relógio.Ao separar a captura de entrada da atualização de saída, o estágio de escravo garante que a saída permaneça estável até que o estágio mestre tenha processado totalmente a entrada.Isso impede quaisquer alterações prematuras ou não intencionais na saída durante o ciclo do relógio.

Por que a configuração do escravo principal é importante?

O processo de dois estágios estabiliza a operação do flip-flop JK, impedindo oscilações ou flutuações indesejadas que podem acontecer em configurações mais simples, especialmente quando ambos os entradas são mantidos altos.Ao dissociar o processamento de entrada da alteração da saída, a configuração principal da escrava garante que as saídas permaneçam previsíveis e estáveis, mesmo em situações em que o tempo é valioso.

Abordando a corrida em torno da condição em jk flip-flops

As condições de corrida ocorrem nos chinelos JK quando ambas as entradas, J e K, são altas e o sinal do relógio permanece ativo por muito tempo.Isso leva à alternância contínua das saídas, o que pode causar comportamento irregular e interromper a confiabilidade do circuito.

A configuração do escravo principal usa um processo de duas etapas para evitar problemas de corrida.O estágio mestre captura os valores de entrada na borda do relógio e os trava. O estágio do escravo atualiza as saídas na próxima borda do relógio, garantindo que a saída não mude até que as entradas sejam totalmente processadas.Essa abordagem impede efetivamente que a saída altere incontrolavelmente, mesmo que as entradas permaneçam altas por um período prolongado.

Outro método para evitar condições de corrida de corrida é ajustar a duração do pulso do relógio.Ao tornar o relógio mais curto que o atraso de propagação do flip-flop, você pode garantir que o estado não mude mais de uma vez no mesmo ciclo do relógio.Isso impede que o flip-flop alterne repetidamente durante um único ciclo, estabilizando a saída.

Dinâmica da troca de flip-flops JK

O comportamento de comutação de um flip-flop JK é amplamente acionado pelo tempo do sinal do relógio e pelos níveis de entrada (J e K).O flip-flop altera o estado com base nas entradas presentes na borda positiva do sinal do relógio.Nesse momento perigoso, o flip-flop avalia as entradas e atualiza sua saída de acordo.

Quando o sinal do relógio atinge a borda ascendente, o jk flip-flop lê os estados atuais das entradas J e K.Dependendo de seus valores, o flip-flop manterá, definirá, definirá, redefinirá ou alternará sua saída.

Relógios digitais: A precisão é tudo em relógios digitais, e os chinelos JK ajudam a manter essa precisão, garantindo que as mudanças de estado ocorram apenas em intervalos precisos do relógio.

Testadores lógicos seqüenciais: Nos sistemas que testam a funcionalidade dos circuitos lógicos, os flip-flops JK desempenham um papel na verificação de que cada componente responde corretamente a sinais cronometrados específicos.

Outros sistemas sensíveis ao tempo: Em várias aplicações digitais em que o tempo é arriscado, como sistemas de comunicação ou unidades de processamento de dados, o FLIP-FLOP JK garante que as transições de estado ocorram sincronizadas com o relógio, impedindo os erros de tempo.

Conclusão

O JK Flip-Flop se destaca como um elemento final no design do circuito digital, oferecendo uma mistura de versatilidade e precisão desesperada por uma ampla variedade de aplicações que variam do armazenamento de memória à divisão de frequência e sincronização de processos digitais.Sua capacidade de mitigar as condições de raça por meio de configurações inovadoras, como o arranjo de escravos principais, ressalta sua adaptabilidade na resolução de desafios inerentes ao design.Da mesma forma, o grave papel do Flip-Flop na garantia de transições precisas do estado destacam sua natureza necessária na criação e manutenção de sistemas digitais confiáveis e eficientes.À medida que a tecnologia avança, os projetos e aplicações em evolução do FLIP-FLOP JK continuam a ser fundamentais para ultrapassar os limites da eletrônica digital para arquiteturas mais sofisticadas e robustas.

Perguntas frequentes [FAQ]

1. Quais são as aplicações do Flip Flop JK?

O FLIP-FLOP JK é usado extensivamente em eletrônicos digitais para uma variedade de tarefas:

Aplicações de tempo: Pode servir como um elemento de atraso ou um cronômetro quando conectado em determinadas configurações.

Contadores e registros: Ao alternar seu estado com cada pulso de relógio, ele é usado no design de vários contadores e registros de turnos que são finais em circuitos lógicos seqüenciais.

Armazenamento de memória: Ele fornece uma unidade básica de armazenamento de memória, útil para armazenar bits em aplicativos computacionais.

2. Como funciona um jk flip-flop com uma tabela de verdade?

Um flip-flop JK tem duas entradas (J e K) e um sinal de relógio.Sua operação varia de acordo com os estados de entrada, sincronizados com o relógio:

• j = 0, k = 0: a saída não muda.

• j = 0, k = 1: a saída é redefinida para 0.

• j = 1, k = 0: a saída é definida como 1.

• j = 1, k = 1: a saída alterna (ou seja, se for 0, torna -se 1 e vice -versa).

3. O que é JK Flip Flop e está funcionando?

Um flip-flop JK combina as propriedades dos flip-flops SR e T.Evita a condição "proibida" vista nos chinelos de SR usando as entradas JK de maneira eficaz:

O estado do flip-flop é controlado pelas entradas J e K, que determinam se a saída deve manter, redefinir, definir ou alternar, em sincronia com a borda subindo ou descendente do pulso do relógio.

4. Quais são as aplicações de travas e flip-flops?

Armazenamento de dados: As travas e os flip-flops são graves para armazenamento de dados em registros e matrizes de memória.

Divisão de Frequência: Usado em divisores de frequência devido à sua capacidade de alterar os estados nas bordas do relógio, pela metade a frequência a cada estágio de uma série.

Máquinas de Estado: Básico no design de máquinas de estado finitas que são usadas para implementar a lógica seqüencial e os circuitos de controle.

Debouncing: Usado para estabilizar sinais de interruptores e botões mecânicos, garantindo transições simples e limpas.

5. Para que os flip-flops são usados?

Armazenamento binário: Cada flip-flop armazena um pouco de dados, tornando-os blocos de construção para dispositivos de armazenamento binário.

Divisores de relógio: Eles dividem a frequência do relógio de entrada por dois, úteis em relógios digitais e aplicativos de tempo.

Sobre Nós

ALLELCO LIMITED

Consulte Mais informação

Inquérito rápido.

Por favor, envie uma consulta, responderemos imediatamente.

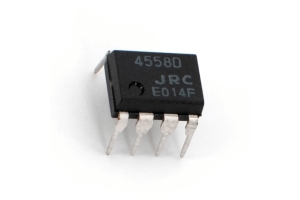

JRC4558 OP-AMP: RECURSOS, ESPECIFICAÇÕES E APLICAÇÕES

em 18/09/2024

330 ohm resistor e códigos de cores

em 13/09/2024

Postagens populares

-

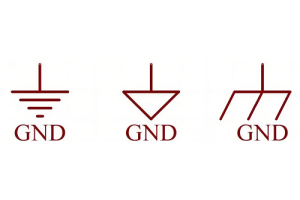

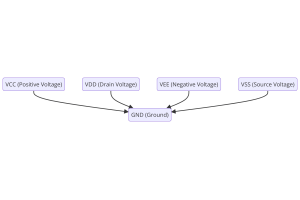

O que é GND no circuito?

em 01/01/1970 2953

-

Guia do conector RJ-45: Códigos de cores do conector RJ-45, esquemas de fiação, aplicativos R-J45, folhas de dados RJ-45

em 01/01/1970 2505

-

Tipos de conector de fibra: SC vs LC e LC vs MTP

em 01/01/1970 2095

-

Entendendo tensões da fonte de alimentação em eletrônicos VCC, VDD, VEE, VSS e GND

em 09/11/0400 1902

-

Comparação entre DB9 e RS232

em 01/01/1970 1767

-

O que é uma bateria LR44?

A eletricidade, essa força onipresente, permeia silenciosamente todos os aspectos de nossas vidas diárias, desde aparelhos triviais até equipamentos médicos com risco de vida, ela desempenha um papel silencioso.No entanto, entender verdadeiramente essa energia, especialmente como armazenar e gerá -la com eficiência, não é uma tarefa fácil.É nesse contexto que este artigo se concentrará ...em 01/01/1970 1715

-

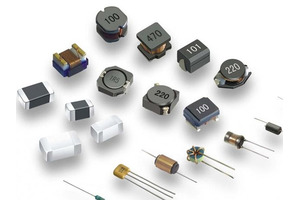

Compreendendo os fundamentos: resistência à indutância e capacitância

Na intrincada dança da engenharia elétrica, um trio de elementos fundamentais leva o centro do palco: indutância, resistência e capacitância.Cada um possui características únicas que ditam os ritmos dinâmicos dos circuitos eletrônicos.Aqui, embarcamos em uma jornada para decifrar as complexidades desses componentes, para descobrir seus papéis distintos e usos práticos dentro da vasta or...em 01/01/1970 1665

-

Guia abrangente da bateria CR2430: Especificações, aplicações e comparação com baterias CR2032

O que é a bateria CR2430?Benefícios das baterias CR2430NormaAplicações de bateria CR2430CR2430 equivalenteCR2430 vs CR2032Tamanho da bateria CR2430O que procurar ao comprar o CR2430 e equivalentesFolha de dados PDFPerguntas frequentes As baterias são o coração de pequenos dispositivos eletrônicos.Entre os muitos tipos disponíveis, as células da moeda desempenham um papel crucial, comumen...em 01/01/1970 1573

-

O que é RF e por que o usamos?

A tecnologia de radiofrequência (RF) é uma parte essencial da comunicação sem fio moderna, permitindo a transmissão de dados em longas distâncias sem conexões físicas.Este artigo investiga o básico da RF, explicando como a radiação eletromagnética (EMR) torna possível a comunicação de RF.Exploraremos os princípios do EMR, a criação e o controle dos sinais de RF e seus usos abrang...em 01/01/1970 1553

-

CR2450 vs CR2032: A bateria pode ser usada?

As baterias de lítio de manganês têm algumas semelhanças com outras baterias de lítio.Alta densidade de energia e vida útil longa são as características que eles têm em comum.Esse tipo de bateria ganhou a confiança e o favor de muitos consumidores por causa de sua segurança única.Gadgets de tecnologia caros?Pequenos aparelhos em nossas casas?Olhe em volta e você os verá em todos os l...em 01/01/1970 1520