Mastering SR Latches: símbolos, funções e aplicações práticas

Uma trava SR é um circuito assíncrono que opera independentemente dos sinais de relógio, tornando -o uma ferramenta versátil em vários aplicativos.Ele mantém um estado binário - alto (1) ou baixo (0) - e pode armazenar um único pedaço de informação, que mantém até que novos sinais de entrada ditem uma alteração.Este elemento básico de armazenamento binário é construído usando dois portões lógicos entre acoplamento, tipicamente nem portões de NAND.A entrada (s) de definição ativa a trava, definindo a saída (q) para alta, enquanto a entrada de redefinição (r) define a saída como baixa.No entanto, altos sinais simultâneos em ambos os insumos levam a um estado indefinido, uma condição que os projetistas devem evitar.As travas SR não são apenas construções teóricas;Eles são implementados em sistemas práticos para manter dados temporários, suportar resultados de processamento intermediário e até gerenciar a detecção de erros em aplicativos críticos, como dispositivos aeroespaciais e médicos, mostrando sua indispensabilidade no design de circuitos digitais.Catálogo

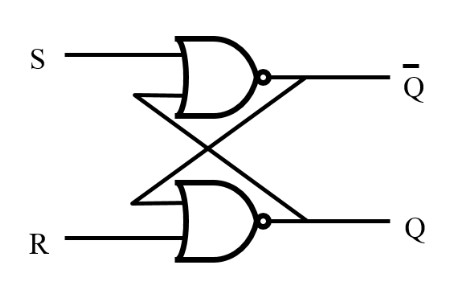

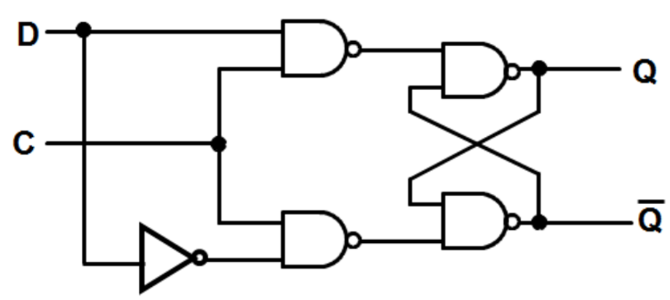

Figura 1: trava SR

O que é uma trava SR?

Uma trava SR, ou trava de retenção de conjunto, é um elemento de armazenamento binário básico que pertence à categoria de circuitos assíncronos.Ao contrário dos circuitos síncronos, as travas SR operam sem um sinal de relógio, confiando apenas no controle direto dos sinais de entrada.Isso permite que eles funcionem de forma independente nos circuitos digitais.Uma trava SR pode manter dois estados estáveis: alta (1) e baixa (0), permitindo armazenar um único pedaço de informação até ser atualizado por novos sinais de entrada.

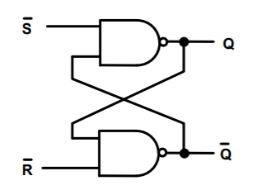

A construção de uma trava SR normalmente envolve dois portões lógicos cruzados, geralmente nem portões ou portões de Nand.Em um design de trava SR usando o Nor Gates, a saída de cada porta é conectada à entrada do outro, formando um loop de feedback.Essa configuração garante que a trava possa alterar rapidamente os estados com base nos sinais de entrada, mantendo a estabilidade até que uma nova entrada solicite uma alteração.

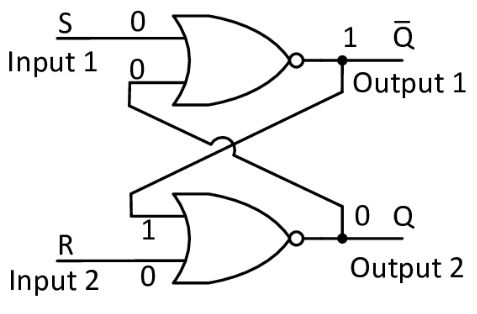

Figura 2: trava SR (2)

Definir entrada (s): Quando a entrada (s) definida é ativada (alta), a saída de trava (q) é alterada para o alto (1).

Redefinir entrada (r): Quando a entrada de redefinição (r) é ativada (alta), a saída (q) muda para baixa (0).

Ambas as entradas altas: se as entradas S e R forem altas simultaneamente, a trava entra em um estado indefinido, que deve ser evitado em design.

As travas SR são essenciais para armazenamento temporário de dados e resultado intermediário em sistemas digitais.Eles são os elementos fundamentais em circuitos seqüenciais mais complexos, como registros de mudança de vários bits, unidades de memória e certos tipos de contadores.

Nesses aplicativos, as travas SR fornecem retenção estável de dados e podem responder rapidamente a alterações em sinais externos, garantindo a operação eficiente de todo o sistema eletrônico.

Outra aplicação crítica das travas SR é a lógica de detecção e correção de erros nos circuitos digitais.Devido à sua capacidade de manter um estado estável, eles podem monitorar as alterações do status do sistema e reverter rapidamente para um estado seguro predefinido após a detecção de uma anomalia.Esse recurso é particularmente valioso em sistemas de alta confiabilidade, como dispositivos aeroespaciais e médicos.

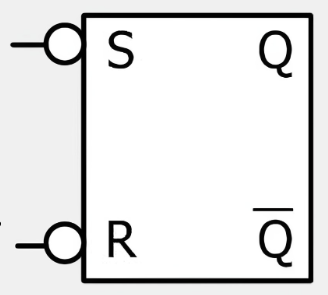

Símbolo da trava SR

Compreender seu símbolo e estrutura é fundamental para entender sua operação e uso prático.Nos diagramas de circuito, a trava SR normalmente possui duas portas de entrada principais marcadas S (Set) e R (Reset).Essas entradas controlam o estado de saída da trava, comumente representado como Q. Alguns projetos também apresentam a saída inversa, marcada Q ', que fornece o estado oposto de Q.

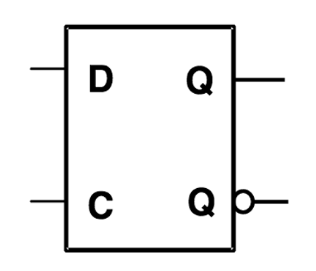

Figura 3: Símbolo da trava SR

Uma trava SR é frequentemente representada por um símbolo retangular com entradas S e R e uma saída Q. Em alguns casos, a saída Q 'também é mostrada.Essa marcação clara permite que os projetistas de circuitos identifiquem rapidamente a função do componente e sua função no circuito maior.

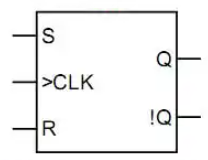

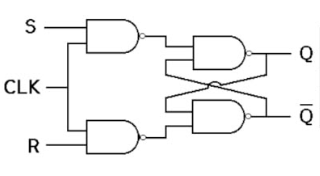

Uma variante comum da trava SR inclui uma entrada de relógio (CLK).A entrada CLK garante que as alterações de estado ocorram sincronizadas com o sinal do relógio, permitindo o controle preciso do tempo.Nesta configuração, mesmo que S ou R sejam ativados, o estado da trava apenas atualiza quando o sinal CLK atende a condições específicas, geralmente na borda de ascensão ou queda.Isso evita erros causados por falhas de sinal de entrada ou alterações não intencionais.

Figura 4: Símbolo da trava SR do relógio

O símbolo de trava SR com relógio inclui as entradas S, R e CLK dentro de um retângulo.Essa representação padronizada ajuda os designers a entender a funcionalidade da trava e seus requisitos de tempo.Por exemplo, em computação de alto desempenho ou sistemas de transferência de dados complexos, o controle CLK cuidadoso garante que os dados sejam armazenados e transferidos com precisão em cada estágio de processamento, otimizando o desempenho e a confiabilidade gerais do sistema.

O controle preciso das entradas de trava de SR é importante, principalmente na criação de memória de alta e grande capacidade ou buffers de dados temporários.Ao projetar circuitos lógicos para gerenciar a ativação de S e R, podem ser alcançadas funções complexas, como carregamento de dados, limpeza ou redefinição de estado.O controle preciso do sinal CLK garante que todas as operações de dados sigam uma sequência de tempo predefinida, aumentando significativamente a eficiência do sistema e a capacidade de processamento de dados.

Uma compreensão profunda do símbolo e estrutura da SR Latch ajuda não apenas no projeto correto de circuitos e na solução de problemas, mas também na execução de operações lógicas digitais complexas e na melhoria do desempenho do sistema.Isso é especialmente crítico em aplicações que requerem alta confiabilidade e controle preciso, como dispositivos aeroespaciais e médicos.

Tipos de trava e seus princípios de trabalho

As travas são componentes fundamentais no design eletrônico, oferecendo diversas funções e aplicações amplas.Os principais tipos de trava são travas SR e travas D, cada uma com operações exclusivas e casos de uso.

Trava SR

A trava SR, ou trava de retenção de conjunto, é um dispositivo de armazenamento básico controlado por suas duas entradas, S (Set) e R (Reset).

Quando a entrada S recebe um sinal alto, a saída Q fica alta, indicando que os dados estão definidos.Quando a entrada R recebe um sinal alto, a saída Q se torna baixa, indicando que os dados são redefinidos.Se as entradas S e R forem altas simultaneamente, a trava entrará em um estado indefinido, causando potencial instabilidade de saída.Esta condição deve ser evitada no design.A resposta direta do SR Latch aos sinais de entrada o torna útil em situações que exigem reação rápida.

D trava

A trava d, também conhecida como trava de dados ou trava transparente, oferece controle mais complexo com entrada de dados D e Clock Signal CLK.

Figura 5: D trava

Figura 6: s símbolo de trava

Quando o CLK está alto, a saída Q segue a entrada D, permitindo que os dados passem pela trava livremente.Quando o CLK diminui, o valor atual de D é bloqueado e a saída q permanece constante até o próximo sinal CLK alto.Esse mecanismo torna a trava D ideal para armazenar temporariamente dados para sincronizar diferentes velocidades de processamento dentro de um sistema.

As travas SR e D têm uma função incomparável no armazenamento de dados e na lógica da máquina de estado.Devido à sua resposta direta no nível de entrada, as travas são essenciais no projeto de circuitos assíncronos.Eles fornecem funções vitais para transferências de dados complexas e sistemas de gerenciamento de energia, armazenando efetivamente informações de estado para garantir uma operação estável.O uso adequado dessas travas pode melhorar significativamente a confiabilidade e a eficiência do circuito, tornando -as indispensáveis nos sistemas eletrônicos modernos.

Tabela de verdade de uma trava SR

Figura 7: SR NAND LATCH

|

S |

R |

Q |

Q ' |

Observação |

|

0 |

0 |

1 |

1 |

PROIBIDO |

|

0 |

1 |

1 |

0 |

DEFINIR |

|

1 |

0 |

0 |

1 |

REINICIAR |

|

1 |

1 |

Q |

Q ' |

Reter |

Gráfico 1: Tabela de verdade da trava SR usando portões NAND

Figura 8: sr nem trava

|

S |

R |

Q |

Q ' |

Observação |

|

0 |

0 |

Q |

Q ' |

Reter |

|

0 |

1 |

1 |

0 |

REINICIAR |

|

1 |

0 |

0 |

1 |

DEFINIR |

|

1 |

1 |

0 |

0 |

PROIBIDO |

Gráfico 2: Tabela de verdade da trava SR usando Nor Gates

Agora, pegamos a tabela de verdade da trava SR usando o NOR NOR como exemplo para entender o significado da tabela de verdade da trava SR.

Estados de entrada e saída

S e R são 0: a trava permanece em seu estado atual.A saída Q permanece a mesma, seja 0 ou 1.

S IS 0 e R é 1: A trava é redefinida, forçando a saída Q a 0.

S IS 1 e R é 0: a trava conjunta, tornando a saída q igual a 1.

S e R são 1: essa condição é inválida ou indefinida, muitas vezes chamada de estado "proibido" em uma trava SR.Nesse caso, q e q 'são iguais 0, levando a uma saída ambígua.

Quando S e R são 0, a trava não faz nada e simplesmente mantém seu valor atual.Isso é útil para manter o estado sem alterações.

Quando S é 0 e R é 1, a trava é explicitamente instruída a redefinir, certificando -se de que Q seja 0, independentemente de seu estado anterior.Esta é uma maneira direta de limpar a trava.

Quando S é 1 e R é 0, a trava é definida, garantindo que Q se torne 1. É assim que você armazena um '1' na trava.

Quando S e R são 1, o estado não é permitido porque faz com que ambas as saídas sejam 0, o que é contraditório e não confiável.Os designers devem evitar essa condição para garantir uma operação estável.

Vantagens e desvantagens das travas

As travas são amplamente utilizadas no design do circuito digital devido à sua simplicidade e baixo custo.Essas características permitem que as travas operem em altas velocidades com baixo consumo de energia, tornando-as ideais para sistemas digitais de alta velocidade.Por exemplo, nos arquivos de registro do processador, as travas podem armazenar e recuperar rapidamente dados, aumentando significativamente a velocidade e a eficiência do processamento.

Vantagens de travas

Simplicidade e custo-efetividade: as travas são componentes diretos que são baratos para implementar em circuitos digitais.

Alta velocidade e baixa potência: seu design permite uma operação rápida com o mínimo de consumo de energia, o que é crítico em sistemas digitais de alta velocidade.

Eficiência no manuseio de dados: em aplicativos como arquivos de registro do processador, as travas fornecem armazenamento e recuperação de dados rápidos, aprimorando o desempenho geral do sistema.

Desvantagens das travas

Apesar de suas vantagens, as travas têm limitações notáveis em certos projetos e aplicações.

Comportamento imprevisível em projetos assíncronos: sem o controle do sinal do relógio, as travas podem se comportar imprevisivelmente.Nas travas SR, se as entradas de conjunto (s) e redefinir (r) forem altas simultaneamente, a saída se tornar indefinida, levando à instabilidade.Isso é problemático em aplicações de controle em tempo real ou críticas de segurança, onde a saída confiável é crucial.

Design de tempo complexo: o design com travas requer considerações cuidadosas de tempo.Os engenheiros devem explicar os atrasos na propagação do sinal e as condições de corrida para evitar erros de tempo.O design inadequado pode resultar em alterações de dados antes que o sinal do relógio se estabilize, causando corrupção de dados ou captura incorreta de dados.Isso requer uma profunda compreensão da análise de tempo e do comportamento do circuito.

Para enfrentar esses desafios, podem ser empregadas técnicas e estratégias específicas de design:

Mecanismos de sincronização: Adicionar mecanismos de sincronização pode ajudar a gerenciar entradas assíncronas e mitigar o comportamento imprevisível.

Gerenciamento de relógio personalizado: a implementação de estratégias de gerenciamento de relógio personalizadas pode garantir que os dados sejam travados corretamente e nos momentos certos.

Uso de ferramentas EDA: as ferramentas modernas de automação de design eletrônico (EDA) oferecem análises avançadas e recursos de otimização.Essas ferramentas ajudam a prever e resolver problemas de tempo e sincronização durante a fase de design, melhorando a confiabilidade e o desempenho dos sistemas digitais usando travas.Eles ajudam os designers a identificar possíveis problemas com antecedência, garantindo que o produto final opere de maneira confiável sob várias condições.

Aplicações práticas de travas SR

As travas SR, conhecidas por sua capacidade de manter o estado de maneira rápida e confiável, são amplamente utilizadas em vários sistemas eletrônicos.Eles se destacam em cenários que exigem armazenamento temporário de dados ou retenção de estado.

Armazenamento de dados temporários

As travas SR são frequentemente usadas na memória de cache para armazenar temporariamente os dados.Isso permite que o sistema acesse rapidamente dados usados com frequência, aumentando significativamente os recursos de processamento de dados e a eficiência dos processadores em larga escala.

Arquivos de registro de armazenamento

Nos processadores, as travas SR permitem armazenamento rápido e recuperação de dados nos arquivos de registro, aprimorando a velocidade de processamento e o desempenho geral do sistema.

Mantendo sinais de controle

Nos sistemas de controle digital, as travas SR são úteis para manter o estado de certos sinais de controle até que as condições externas ou a lógica do sistema determinem uma alteração.Além disso, eles ajudam na retenção de estados dentro do sistema, garantindo um desempenho consistente em operações que requerem precisão e confiabilidade.

Gatilho e contra -circuitos

Os flip-flops baseados em trava SR são comumente usados em circuitos que requerem operação sincronizada, como relógios e temporizadores digitais.Eles controlam pulsos de contagem, garantindo cronometragem precisa e desempenho confiável.Esses circuitos dependem de travas SR para manter contagens precisas, o que facilita o tempo e o sequenciamento em sistemas digitais.

Interações mecânicas

As travas SR são eficazes na eliminação do salto mecânico nos interruptores.Um salto mecânico ocorre quando um comutador gera mudanças rápidas de sinal repetitivo devido ao mau contato.As travas SR estabilizam o sinal de saída, impedindo erros causados por sinais barulhentos.

SR FLIP-FLOP

Um flip-flop SR, frequentemente chamado de flip-flop acionado por arestas, consiste em duas travas SR interconectadas.Essa estrutura de trava dupla permite que ela responda a bordas específicas do sinal do relógio (subindo ou descendo) para alterar seu estado.Isso é alcançado através do controle lógico especial entre as travas.A saída da primeira trava se torna parte da entrada da segunda trava e a saída da segunda trava, por sua vez, influencia a primeira trava, criando um loop de feedback entrelaçado.

Figura 7: SR FLIP-FLOP

O flip-flop do SR muda de forma precisamente na borda subindo ou descendo do sinal do relógio.O feedback interligado entre as duas travas SR garante que o flip-flop altere apenas o estado em resposta à borda do relógio, fornecendo saída estável e confiável.

Nos microprocessadores e processadores de sinal digital, os flip-flops SR são usados para amostragem e armazenamento de dados.Eles capturam e estabilizam dados nas bordas do relógio especificadas, garantindo processamento e análise de dados subsequentes confiáveis.

O mecanismo de acionamento de arestas ajuda a evitar condições de corrida, onde diferentes partes do circuito podem alterar o estado ao mesmo tempo sem sincronização, resultando potencialmente em saídas instáveis ou incorretas.Os flip-flops de SR são cruciais na implementação da lógica de protocolo de comunicação específica, como sincronização de quadros e detecção de erros.Sua estabilidade e tempo de resposta rápido ajudam a manter a qualidade da transmissão de dados e a confiabilidade do sistema.

Estados proibidos em travas SR e chinelos de SR

Ao projetar travas SR e chinelos de SR usando NAND e NOR GATES, todos precisamos prestar atenção ao gerenciamento e evitando estados inibidos.Um estado proibido ocorre quando as entradas de conjunto (s) e redefinir (r) são simultaneamente altas (para portões NAND) ou baixos (para portões não.Essa combinação leva a um estado de saída indeterminado, pois a saída depende do estado anterior do circuito, tornando -o imprevisível.

Estados proibidos em Nand Gate SR Breathes

Quando S e R são baixos, ambas as saídas aumentam, o que viola a característica complementar da saída da trava.Isso resulta em um estado indeterminado.

Estados proibidos em Nor Gate Sr Batches

Quando S e R são altos, ambas as saídas ficam baixas, criando também um estado indeterminado.Isso pode levar a um comportamento imprevisível no circuito.

Abordagens práticas para evitar estados proibidos

Adicionando lógica de controle

Use portões lógicos adicionais para monitorar os estados de S e R. Se ambos os entradas tenderem a um estado proibido, ajuste automaticamente uma entrada para evitar o estado indeterminado.Isso garante que as saídas permaneçam estáveis e previsíveis.Implemente um portão lógico que intervém quando S e R são altos (ou baixos), ajustando uma entrada para manter um estado válido.

Simulação de software e teste de hardware

Realize simulações completas de software para identificar potenciais estados proibidos sob várias condições operacionais.Isso permite que os designers localizem e corrige erros lógicos antes da implementação física.Execute um extenso teste de hardware para validar que o circuito lida com todas as combinações de entrada corretamente.Esta etapa ajuda a garantir que a trava ou o flip-flop opere de maneira confiável em cenários do mundo real.

Conclusão

A versatilidade e confiabilidade das travas SR destacam seu significado no design do circuito digital.Ao explorar o comportamento diferenciado da SR trava através de suas representações de símbolos, tabelas de verdade e aplicações práticas, obtemos uma compreensão abrangente de sua operação e importância.Apesar das possíveis armadilhas de estados indefinidos em projetos assíncronos, a implementação estratégica da lógica de controle e a extensa simulação podem mitigar esses riscos.As ferramentas avançadas de automação de design eletrônico (EDA) aprimoram ainda mais a confiabilidade e o desempenho dos circuitos que incorporam travas SR prevendo e resolvendo problemas de tempo e sincronização.Seja usado em armazenamento temporário de dados, manutenção de sinal de controle ou detecção de erros, as travas SR provam ser fundamentais na criação de sistemas digitais robustos e eficientes.Seu papel nas operações de memória de alta velocidade e no processamento de dados síncronos em aplicativos complexos exemplifica sua relevância duradoura.À medida que a tecnologia avança, os princípios que regem as travas SR continuam a informar e inspirar inovações em eletrônicos digitais, garantindo que esses componentes elementares permaneçam parte integrante do desenvolvimento de dispositivos eletrônicos sofisticados e confiáveis.

Perguntas frequentes [FAQ]

1. O que é uma trava SR?

Uma trava SR, ou trava-reset de conjunto, é um elemento de armazenamento binário fundamental usado em circuitos digitais.É um circuito assíncrono, o que significa que opera sem um sinal de relógio, contando com o controle direto de suas entradas para alterar os estados.

2. Qual é a função do SR na lógica?

Na lógica, as entradas SR (Set-Reset) controlam o estado da trava.

3. Que tipo de portão lógica uma trava SR usa?

Uma trava SR normalmente usa portões nem portões ou portões NAND.Em uma trava de SR baseada em NOR, a saída de cada portão NOR é alimentada de volta à entrada do outro, criando um loop de feedback estável.Em uma trava de SR baseada em Gate, uma configuração de feedback semelhante é usada, mas os níveis lógicos são invertidos em comparação com a trava baseada em gate.Ambas as configurações atingem a mesma funcionalidade básica de manter um estado binário com base nas entradas de conjunto e redefinir.

4. Como funciona uma trava?

Uma trava funciona usando feedback para manter seu estado de saída com base nas entradas fornecidas.Em uma trava SR, as entradas de conjunto (s) e redefinir (r) controlam o estado da saída (q).Quando a entrada definida é ativada (alta), a saída é definida como alta (1).Quando a entrada de redefinição é ativada (alta), a saída é redefinida para baixa (0).O loop de feedback no design da trava garante que, uma vez que um estado de saída seja estabelecido, ele permanece estável até que um novo sinal de entrada o altere.

5. Qual é a desvantagem com uma trava SR?

A desvantagem primária de uma trava de SR é o estado indefinido que ocorre quando as entradas definidas e redefinidas (r) são altas simultaneamente.Essa condição leva a um estado de saída indeterminado, que pode causar instabilidade e comportamento imprevisível nos circuitos digitais.Esse estado "proibido" deve ser evitado em design para garantir uma operação confiável.

Trava de SR, trava de conjunto de conjunto, circuito assíncrono, elemento de armazenamento binário, circuitos digitais, nem portões, portões NAND, ciclo de feedback, alto estado, baixo estado, estado indefinido, sinal de relógio, controle direto, armazenamento temporário de dados, retenção de resultados intermediários,Detecção de erros, aplicações aeroespaciais, dispositivos médicos, design de circuitos, trava SR com relógio, sinais de entrada, símbolo e estrutura, memória de alta velocidade, buffers de dados, controle de tempo, controle preciso, retenção de estado, microprocessadores, processadores de sinal digital, amostragem de dados, dadosArmazenamento, desperdício de arestas, flip-flop, feedback interligado, condições de corrida, lógica do protocolo de comunicação, sincronização de quadros, detecção de erros, falhas de sinal, automação de design eletrônico, ferramentas de EDA, mecanismos de sincronização, gerenciamento de relógio personalizado, erros de tempo, atrasos de propagação,Condições de raça, transferências de dados complexas, sistemas de gerenciamento de energia, rejeição mecânica, aplicações práticas, sistemas de controle digital, portões de lógica, simulações de software, teste de hardware, estados proibidos, confiabilidade da trava.