Compreendendo o poder da trava S-R: uma porta de entrada para a eletrônica moderna

As travas são dispositivos digitais simples que armazenam um pouco de informação e mantêm esse valor até obter novos sinais de entrada.Eles são usados em sistemas digitais para manter temporariamente os dados binários.As travas podem ser feitas usando diferentes tipos de portões lógicos básicos, como e, ou não, NAND e nem portões.Este artigo explora o design, a função, as variações e os usos da trava S-R, enfatizando seu melhor papel na eletrônica moderna e seu uso em circuitos práticos e simulações lógicas digitais.

Catálogo

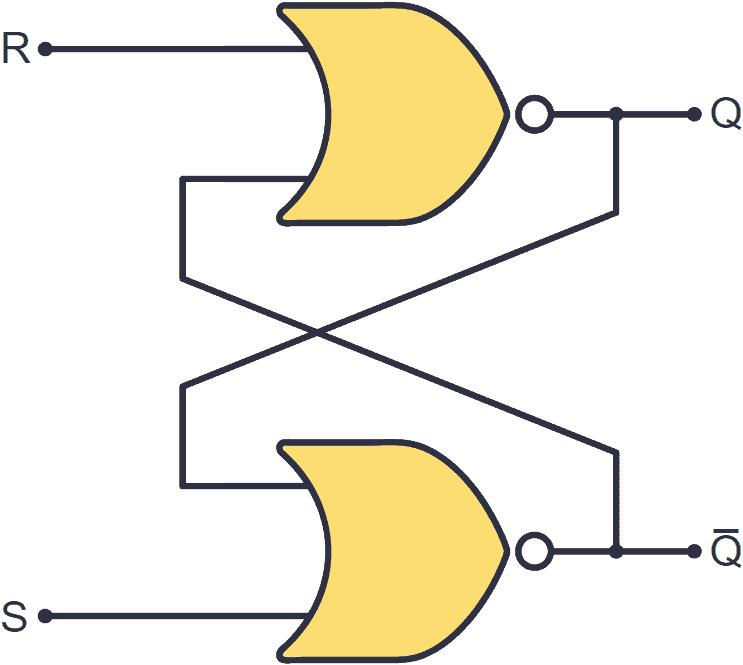

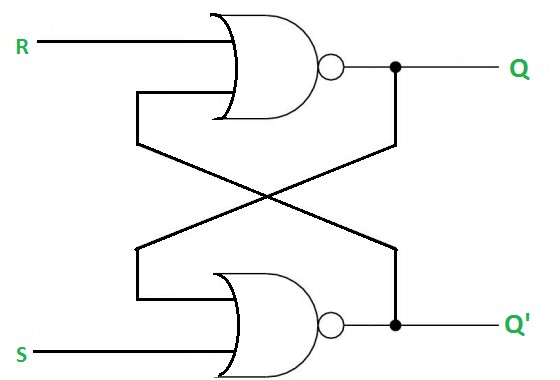

Figura 1: Diagrama de circuito de trava S-R

Estrutura da trava S-R

A trava S-R (Reset Set), uma pedra angular em eletrônicos digitais, é um multivibrador biestível.É capaz de manter um dos dois estados distintos e estáveis indefinidamente sem entrada externa.Essa funcionalidade renderiza a trava SR um componente principal nas operações de armazenamento e comutação de memória em diferentes dispositivos eletrônicos.

Estruturalmente, a trava SR consiste em dois portões interconectados nem dispostos em um design de loop de feedback.Esse arranjo específico é importante, pois oferece os pré -requisitos para a bistabilidade.A saída de cada portão está conectada diretamente à entrada do outro, criando um loop contínuo de feedback que sustenta a operação da trava.

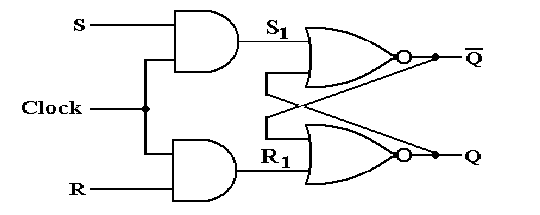

Figura 2: trava S-R e o sinal do relógio (CLK)

Expandindo o design básico, o bloqueio de SR do fechamento apresenta uma entrada adicional: o sinal do relógio (CLK).Esse aprimoramento incorpora uma entrada de relógio que traz camada de controle, integrando as operações de trava em sistemas que requerem sincronização.Essa sincronização obrigada à medida que determina os momentos precisos em que a trava pode alterar os estados, apropriadamente descritos pelo termo "fechado".A inclusão do sinal do relógio garante que as alterações no estado de saída da trava ocorram apenas durante a fase de relógio ativa, normalmente na borda de ascensão ou queda do sinal CLK.

A introdução da entrada CLK não apenas preserva as propriedades da trava SR básica, mas também alinha sua operação com a dinâmica temporal de sistemas digitais maiores.Esse desejo de alinhamento de manter a integridade dos dados e garantir que as transições de estado ocorram sem falhas ou alterações não intencionais, particularmente em configurações complexas de circuitos em que várias travas podem interagir.Ao controlar quando a trava responde aos comandos definidos e redefinidos, o sistema pode evitar problemas como condições de corrida e outros erros relacionados ao tempo que poderiam interromper a estabilidade e o desempenho do sistema.

Estados operacionais da trava S-R

Sua operação depende das entradas de dois sinais de controle: Conjunto (s) e redefinição (R).Aqui, explicamos como essas entradas afetam as saídas e os estados da trava SR.

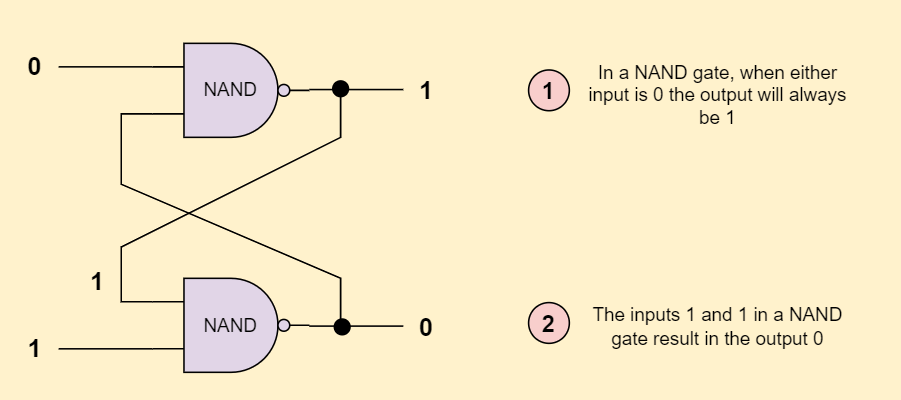

Caso 1: Defina a condição

Quando a entrada do conjunto (s) é alta (1) e a entrada de redefinição (r) é baixa (0), a trava entra na condição de conjunto.Nesse estado, o portão NAND conectado à entrada R produzirá um sinal baixo devido à alta entrada de S. Este sinal baixo faz com que o segundo portão NAND produza um sinal alto, definindo Q para High (1) e Q-Barpara baixo (0).Esse estado é estável e manterá o Q alto até que as entradas mudem, mostrando a capacidade da trava de armazenar um estado alto.

Figura 3: o estado definido

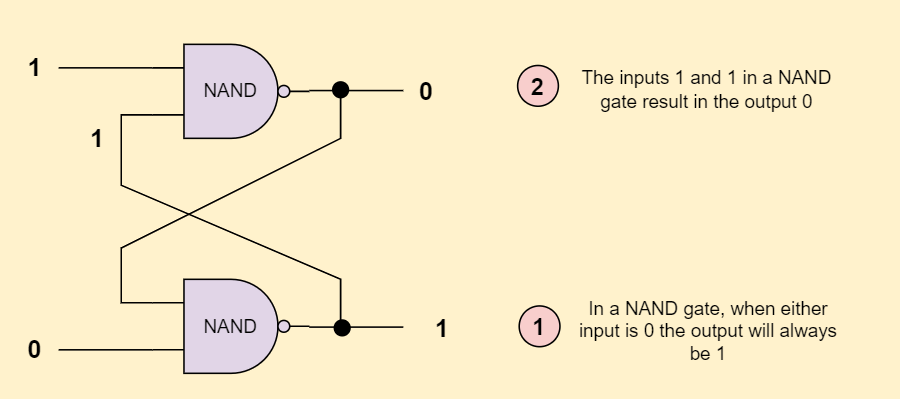

Caso 2: Redefinir condição

Quando S é baixo (0) e R é alto (1), a trava entra na condição de redefinição.Aqui, a alta entrada em R e a baixa entrada em S tornam o portão NAND conectado à saída R um sinal baixo.Esse sinal baixo define Q a baixo (0) e q-bar para alto (1), redefinindo efetivamente a trava.Isso demonstra a capacidade da trava de retornar a um estado baixo estável em q quando recebe as entradas corretas.

Figura 4: o estado de redefinição

Caso 3: estado inválido

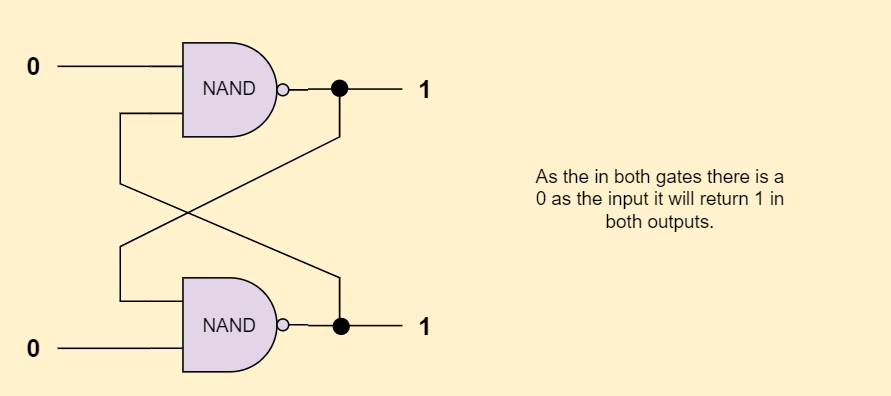

Se S e R forem baixos (0), ambas as entradas para os portões NAND são baixas, fazendo com que ambas as saídas q e q-bar sinalizem alto.Esse estado é chamado de inválido ou proibido porque quebra a regra básica de que Q e Q-Bar sempre devem ser opostos.Esse cenário destaca a limitação da trava SR, enfatizando a importância de evitar estados tão instáveis através do gerenciamento de entrada adequado.

Figura 5: o estado inválido

Caso 4: Mantenha a condição

Quando ambas as entradas são altas (1), as saídas dependem do estado anterior da trava, em vez das entradas atuais.Isso é conhecido como condição de retenção, onde q e q-bar permanecem inalterados, preservando o último estado válido da trava.Para algumas aplicações, é importante poder manter o estado travado por longos períodos de tempo sem modificação, como células de armazenamento de memória onde a integridade dos dados é de alta importância.

Figura 6: o estado de espera

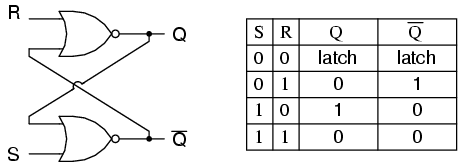

Trava S-R com uma tabela de verdade

Esta tabela não é apenas uma ferramenta teórica, mas também é prática para designers de circuitos e alunos.Isso os ajuda a ver como a trava se comporta sob muitas condições.Abaixo, apresentamos a tabela de verdade abrangente para a trava SR, seguida de explicações e idéias práticas para cada condição.

|

S |

R |

Q |

Q-Bar |

ESTADO |

|

0 |

0 |

1 |

1 |

Inválido |

|

0 |

1 |

0 |

1 |

Reiniciar |

|

1 |

0 |

1 |

0 |

Definir |

|

1 |

1 |

Q |

Q-Bar |

Segurar |

Gráfico 1: SR

Tabela de verdade

Explicação de cada linha

Defina condição (s = 1, r = 0): Esta linha mostra que quando S é alto e R é baixo, q é definido como alto (1) e q-bar para baixo (0).Isso reflete a resposta do circuito a um comando definido, armazenando efetivamente um '1'.

Redefinir condição (s = 0, r = 1): Aqui, as entradas indicam uma operação de redefinição.Consequentemente, q é redefinido para baixo (0) e q-bar é definido como alto (1).Este estado demonstra a capacidade da trava de reverter para um '0'.

Condição inválida (s = 0, r = 0): ambas as saídas ficam altas nessa condição, o que geralmente é evitado porque resulta em ambas as saídas serem idênticas.Isso pode levar à instabilidade ou comportamento indefinido na trava, pois viola a regra de que Q e Q-Bar sempre devem ser opostos.

Manter a condição (s = 1, r = 1): Nesse cenário, a trava mantém seu estado anterior, mostrando sua capacidade de manter o último estado definido, a menos que seja explicitamente ordenado a mudar.

Insights e dicas práticas

Entendendo os resultados: lembre-se sempre de que Q e Q-Bar são ideais.Qualquer desvio dessa regra (como visto na condição inválido) indica um problema ou uma equívoco.

Evitando o estado inválido: é imperativo que os designers tomem cuidado para evitar a situação em que S e R são baixos.A implementação de lógica ou intertravamentos adicionais pode ajudar a prevenir esse estado.

Utilizando a condição de retenção: a condição de retenção pode ser particularmente conveniente em aplicativos que requerem preservação de dados ao longo do tempo.A manutenção da integridade dos dados pode depender de garantir que a trava não entre no estado definido ou redefinido.

Interpretando a tabela de verdade: Ao projetar ou depurar circuitos, faça referência à tabela de verdade para prever como as alterações na entrada afetarão a saída, especialmente em circuitos complexos onde várias travas são usadas.

Dinâmica funcional da trava S-R

A trava S-R (conjunto de conjunto) funciona bem apenas se suas entradas forem gerenciadas corretamente.Para entender como funciona, você precisa saber como as diferentes combinações de entrada afetam as saídas, Q e Q-Bar (o oposto de Q).

Figura 7: trava S-R

Se o conjunto (s) e a redefinição (r) forem ativados ao mesmo tempo (s = 1 e r = 1), a trava entra em um "estado proibido", onde ambas as saídas, q e q-bar, serão 0.Isso é um problema, porque normalmente, Q e Q-Bar devem ser opostos.

Sob condições normais, para definir a trava, você ativa S (defina s como 1) e desative r (defina r a 0).Isso faz com que q fique alto (1) e q-bar diminua (0), mostrando que a trava pode armazenar um 1. Para redefinir a trava, você ativa R (defina r a 1) e desativado s (definido s para 0).Isso faz com que q fique baixo (0) e q-bar sinalize (1), mostrando que a trava pode se limpar e armazenar um 0.

Quando ambas as entradas são desativadas (s = 0 e r = 0), a trava mantém seu último estado, definido ou redefinido.Isso é bom para armazenar dados ou manter um estado sem precisar de entrada contínua.

As condições de corrida podem complicar a operação da trava S-R.Esses erros acontecem quando as saídas dependem muito do momento das alterações de entrada, levando a resultados imprevisíveis se as entradas mudarem quase ao mesmo tempo.Para evitar isso e garantir que a trava funcione de maneira confiável, os mecanismos de atraso de tempo são frequentemente usados.Esses atrasos garantem que uma entrada seja ativada depois que a outra teve tempo de se estabilizar.Para que a trava seja usada em circuitos digitais, onde é necessário um tempo preciso, ela deve executar de forma consistente e manter saídas constantes.Isso é possível pelo tempo controlado.

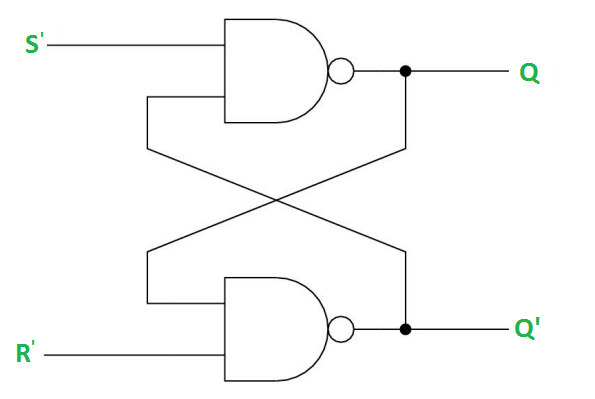

Diagrama lógico da trava S-R

A trava SR é um circuito lógico seqüencial básico com duas configurações principais: nem ou portões NAND.Cada configuração afeta como a trava funciona e responde a entradas, permitindo a personalização para diferentes aplicativos eletrônicos.

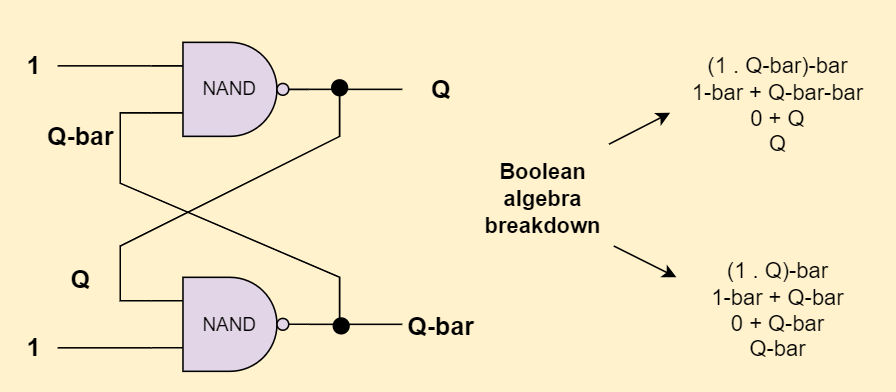

Figura 8: Diagrama lógico representa a trava S-R usando o NAND GATE

Implementação usando portões NAND

Ao construir uma trava de SR com portões NAND, um loop de feedback é usado para manter seu estado.Essa configuração permite que a trava mantenha seu estado anterior quando ambas as entradas (S e R) são baixas.NAND GATES SAÍDA HIL, a menos que ambas as entradas sejam altas.O estado da trava muda quando uma entrada é alta e a outra é baixa.É melhor evitar definir S e R alto ao mesmo tempo, porque isso força as duas saídas a diminuir, levando a um estado indefinido em que as saídas não são mais complementares.O gerenciamento de entrada adequado é uma obrigação para evitar a instabilidade em travas SR baseadas em NAND.

Implementação usando nem portões

O uso de portões NOR para uma trava SR altera as condições operacionais em comparação com os portões NAND.Nesta configuração, a trava mantém seu estado quando ambas as entradas são altas.A trava muda de estado quando uma entrada é baixa e a outra é alta.Nem portões de saída alta somente se ambas as entradas forem baixas.Essa configuração é útil em circuitos em que o estado padrão deve ter ambas as saídas baixas, garantindo uma saída previsível em condições de alta entrada.No entanto, é melhor evitar definir ambos os insumos baixos ao mesmo tempo, pois isso causa saídas conflitantes e reduz a confiabilidade da trava.

Figura 9: o diagrama lógico representa a trava S-R usando o NOR GATE

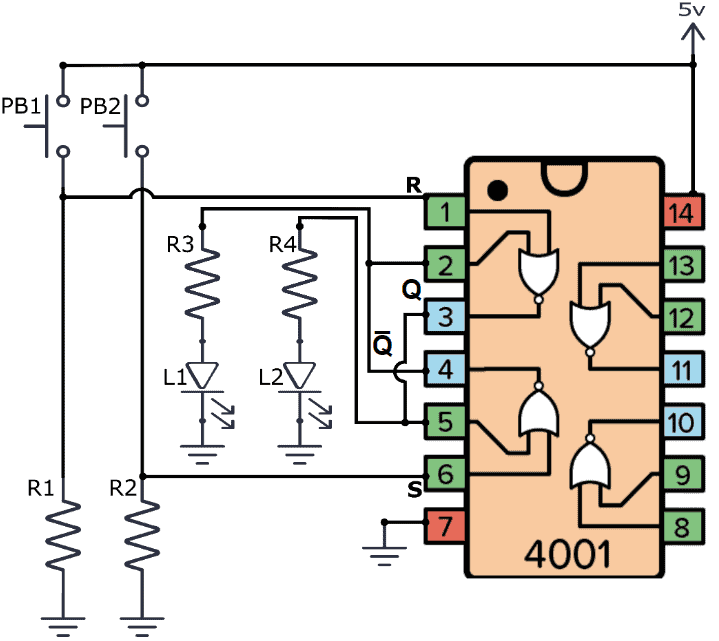

Exemplo de circuito

Explorar como as travas SR funcionam na vida real mostra sua utilidade.Um bom exemplo é um circuito usando o chip CD4001, que possui quatro portões.Este circuito mostra como as travas SR podem controlar dispositivos como LEDs com ações simples, como pressionar botões.

Neste exemplo, o Nor Gates no chip CD4001 é configurado para fazer uma trava SR.Dois portões estão conectados em um loop de feedback para manter o estado de trava.PushButtons são adicionados ao circuito como entrada para definir e redefinir.Pressionar um botão altera o estado da entrada, que altera a trava e o estado de LED.Por exemplo, pressionar o botão definido acende o LED e permanece iluminado mesmo após o lançamento do botão, mostrando como a trava pode manter um estado.

Para melhorar o circuito, mais LEDs podem ser adicionados para mostrar o estado de saída de Q e Q-Bar.Isso facilita a ver como a trava funciona, o que é muito útil nos ambientes de aprendizagem.

Figura 10: trava S-R usando o chip CD4001

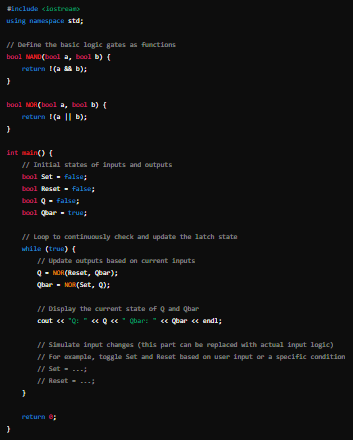

Implementação de código

Traduzir a lógica operacional de uma trava SR em software mostra como o design da lógica digital pode funcionar em hardware e em simulações virtuais.O uso de uma linguagem de programação como C ++ é eficaz porque suporta a lógica e o controle complexos necessários para imitar comportamentos de hardware.

Para fazer uma trava SR em C ++, você começa definindo os portões lógicos básicos como funções que atuam como as versões de hardware.Por exemplo, uma função NAND GATE retornaria o oposto do e operação em suas entradas.Da mesma forma, uma função NOR GATE retornaria o oposto da operação.Com essas funções básicas, você pode modelar o comportamento do SR Latch criando um ciclo de feedback entre essas funções do portão, com base no diagrama de circuito da trava.

O código normalmente teria um loop que verifica continuamente os estados das entradas (definir e redefinir) e atualiza as saídas (q e q-bar) de acordo.As declarações condicionais dentro deste loop determinam como as alterações na entrada afetam as saídas, imitando de perto o comportamento físico da trava de SR.Por exemplo, se as entradas definidas e de redefinição forem baixas, as saídas permanecerão as mesmas.Se o conjunto for alto e a redefinição estiver baixa, a saída q se tornará alta e a barra Q se tornará baixa, replicando a condição definida da trava.

Aqui está um exemplo simples de como isso pode parecer no código:

Figura 11: trava SR em C ++

Esse código configura uma trava SR simples usando nem portões e verifica e atualiza continuamente o estado da trava com base nas entradas.

Aplicações da trava SR

Sistemas de controle nas operações motoras: a trava SR exigida pelos sistemas para controle do motor.Usando interruptores de botão Iniciante (s) e Stop (R), a trava SR mantém um motor funcionando mesmo depois que o botão Iniciar é liberado.Essa configuração garante que o motor funcione continuamente até parar, aumentando a segurança e a conveniência.

Memória e armazenamento de dados: Ao criar circuitos de memória maiores, a trava SR desempenha uma função, pois pode armazenar um único pouco de dados.Ele mantém dados em um estado estável até ser atualizado, formando a base das células de memória na computação digital.

Controle e gerenciamento de sinal: nas aplicações de sinal de controle, as travas SR mantêm bits específicos até que certas condições sejam atendidas, garantindo a sequência e o tempo adequados nas operações.Precisão no processamento de sinal e fluxo de dados dependem disso.

CIRCUITOS DE DEBOMING: As travas SR estabilizam sinais de interruptores e botões mecânicos, impedindo o acionamento falso e os erros causados pelo "salto" quando os interruptores são pressionados.Isso é particularmente adequado em interfaces digitais, como teclados.

Elementos fundamentais em sistemas digitais: o design de flip-flops e contadores, adequados para o tempo e sequenciamento em eletrônicos, depende muito de travas SR.Eles também são usados como travas de pulso para alternar o estado rápido.

Aplicações especializadas: em sistemas assíncronos, variações como a trava D são usadas para transferência de dados segura e confiável.Em sistemas bifásicos síncronos, as travas de dados reduzem a contagem de trânsito, melhorando a eficiência e reduzindo o atraso.

Implicações mais amplas nos eletrônicos: as travas SR são amplamente utilizadas em circuitos de porto de energia, participando da conservação de energia em dispositivos eletrônicos.Eles gerenciam estados de energia em um nível detalhado, contribuindo para a eficiência energética geral dos sistemas digitais.

Conclusão

A trava S-R mostra a importância de estruturas lógicas simples em sistemas digitais complexos.Observando suas diferentes configurações e como funciona, vemos que a trava S-R mantém os dados estáveis e torna os sistemas eficientes e confiáveis.Ele pode funcionar sob várias condições, mostrado por tabelas da verdade e diagramas lógicos, tornando-o adaptável para vários usos, do controle do motor a circuitos digitais básicos, como chinelos e contadores.A trava S-R é adequada em muitas aplicações práticas, como células de memória em computadores e circuitos de debouscing em interfaces digitais, aumentando a eficiência e reduzindo erros em dispositivos eletrônicos.Com mecanismos de feedback e gerenciamento cuidadoso de sinais de entrada, a trava S-R é boa para projetar sistemas digitais mais confiáveis e eficientes.O estudo de sua função através de simulações de software ajuda a conectar a eletrônica teórica com aplicações do mundo real, tornando a trava S-R um tópico importante para engenheiros eletrônicos novos e experientes.

Perguntas frequentes [FAQ]

1. Qual é o objetivo da trava SR?

A trava SR é usada para armazenar um único pouco de dados;É uma forma básica de memória nos circuitos digitais.Sua principal função é manter o estado de um pouco até que seja alterado por sinais de entrada.

2. A trava SR é ativa alta ou baixa?

A trava SR é normalmente ativa, o que significa que responde a entradas altas (nível lógico 1).Quando as entradas s (set) e r (redefinir) são altas, elas acionam alterações na saída.

3. Qual é a desvantagem com uma trava SR?

Uma grande desvantagem da trava SR é sua suscetibilidade a uma condição inválida, onde as entradas de conjunto e redefinir são altas simultaneamente.Essa situação leva a uma saída indefinida, o que pode resultar em comportamento não confiável ou imprevisível.

4. Quais são as regras para a trava SR?

Se S (conjunto) for alto e R (redefinição) for baixo, a saída q é definida como alta.

Se R for alto e S é baixo, a saída q é redefinida para baixa.

Se S e R forem baixos, a saída mantém seu estado anterior.

Se S e R forem altos, a saída será indefinida ou inválida.

5. O que é a memória na trava SR?

A memória em uma trava SR refere -se à sua capacidade de manter o estado de saída (alto ou baixo) indefinidamente, até receber a entrada para alterar o estado.Isso o torna um dispositivo biestável, ideal para armazenamento simples de memória.

6. Quais são as saídas da trava SR?

A trava SR possui duas saídas, q e q '(q-bar).Q representa o estado atual, enquanto Q 'é o inverso de Q. Quando Q é alto, Q' é baixo e vice -versa.

7. Onde usamos a trava?

Quando o armazenamento de dados de curto prazo ou a retenção de estado são necessários, as travas são empregadas em diferentes tipos de aplicações.Isso inclui armazenamento de dados em flip-flops, registros e unidades de memória, bem como em sistemas que requerem sincronização de dados e funções de retenção de circuito.