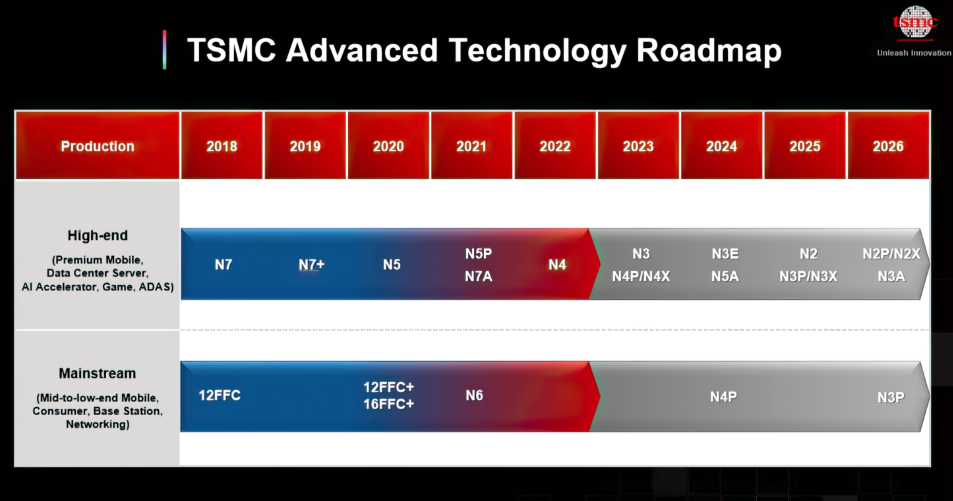

O nó de terceira geração da TSMC está na pista e o N3P será produzido em massa ainda este ano

A TSMC começou com sucesso a usar a tecnologia de processo de nível de segunda geração de 3NM para produzir chips no quarto trimestre de 2023, alcançando o marco planejado.Atualmente, a empresa está se preparando para produzir em massa o desempenho N3P Chips para este nó.A TSMC anunciou no Simpósio Europeu de Tecnologia que isso ocorrerá na segunda metade de 2024.

O processo N3E entrou na produção em massa conforme programado, e a densidade de defeitos é comparável ao processo N5 durante a produção em massa em 2020. O TSMC descreve o rendimento do N3E como "ótimo", e atualmente o único processador que usa N3E - Apple M4- tem significativamenteaumentou o número de transistores e a velocidade do relógio de operação em comparação com o M3 com base na tecnologia N3.

Um executivo da TSMC disse no evento: "A N3E iniciou a produção em massa, conforme planejado no quarto trimestre do ano passado. Vimos um excelente desempenho de produção dos produtos de nossos clientes, então eles realmente entraram no mercado como planejado".

Um executivo da TSMC disse no evento: "A N3E iniciou a produção em massa, conforme planejado no quarto trimestre do ano passado. Vimos um excelente desempenho de produção dos produtos de nossos clientes, então eles realmente entraram no mercado como planejado".

O principal detalhe do processo N3E é sua simplificação em comparação com o processo N3 de primeira geração do TSMC (também conhecido como N3B).Ao remover algumas camadas que requerem litografia EUV e evitando completamente o uso de padronização dupla EUV, o N3E reduz os custos de produção, amplia a janela do processo e melhora o rendimento.No entanto, essas mudanças às vezes reduzem a densidade do transistor e a eficiência de energia, uma troca que pode ser atenuada através da otimização do projeto.

Olhando para o futuro, o processo N3P fornece escala óptica para o N3E e também mostra progresso promissor.Ele passou a certificação de qualificação necessária e mostra o desempenho do rendimento próximo ao N3E.A próxima evolução do portfólio de tecnologia da TSMC visa melhorar o desempenho em até 4% ou reduzir o consumo de energia em cerca de 9% na mesma velocidade do relógio, além de aumentar a densidade do transistor de chips de configuração de design híbrido em 4%.

O N3P mantém a compatibilidade com os módulos IP da N3E, ferramentas de design e métodos, tornando -o uma escolha atraente para os desenvolvedores.Essa continuidade garante que a maioria dos novos designs de chips (chips) deve fazer a transição do uso de N3E para N3P, alavancando o desempenho aprimorado e a eficiência de custos deste último.

O trabalho final de preparação de produção para N3P deve ocorrer no segundo semestre deste ano, quando entrará no estágio HVM (produção em massa).O TSMC espera que os designers de chips o adotem imediatamente.Dadas as suas vantagens de desempenho e custo, o N3P deve ser favorecido pelos clientes da TSMC, incluindo Apple e AMD.

Embora a data exata de lançamento dos chips baseados em N3P ainda seja incerta, espera -se que grandes fabricantes como a Apple usem essa tecnologia em sua série de processadores até 2025, incluindo o SOC para smartphones, computadores pessoais e tablets.

"Também entregamos com sucesso a tecnologia N3P", disse os executivos da TSMC."Foi certificado e seu desempenho de rendimento está próximo da N3E. (Tecnologia do processo) também recebeu as bolachas e a produção dos clientes de produtos começarão na segunda metade deste ano. Devido à N3P (vantagem de PPA), esperamos que a maior parte doAs bolachas no N3 para fluir em direção a N3P. "

Olhando para o futuro, o processo N3P fornece escala óptica para o N3E e também mostra progresso promissor.Ele passou a certificação de qualificação necessária e mostra o desempenho do rendimento próximo ao N3E.A próxima evolução do portfólio de tecnologia da TSMC visa melhorar o desempenho em até 4% ou reduzir o consumo de energia em cerca de 9% na mesma velocidade do relógio, além de aumentar a densidade do transistor de chips de configuração de design híbrido em 4%.

O N3P mantém a compatibilidade com os módulos IP da N3E, ferramentas de design e métodos, tornando -o uma escolha atraente para os desenvolvedores.Essa continuidade garante que a maioria dos novos designs de chips (chips) deve fazer a transição do uso de N3E para N3P, alavancando o desempenho aprimorado e a eficiência de custos deste último.

O trabalho final de preparação de produção para N3P deve ocorrer no segundo semestre deste ano, quando entrará no estágio HVM (produção em massa).O TSMC espera que os designers de chips o adotem imediatamente.Dadas as suas vantagens de desempenho e custo, o N3P deve ser favorecido pelos clientes da TSMC, incluindo Apple e AMD.

Embora a data exata de lançamento dos chips baseados em N3P ainda seja incerta, espera -se que grandes fabricantes como a Apple usem essa tecnologia em sua série de processadores até 2025, incluindo o SOC para smartphones, computadores pessoais e tablets.

"Também entregamos com sucesso a tecnologia N3P", disse os executivos da TSMC."Foi certificado e seu desempenho de rendimento está próximo da N3E. (Tecnologia do processo) também recebeu as bolachas e a produção dos clientes de produtos começarão na segunda metade deste ano. Devido à N3P (vantagem de PPA), esperamos que a maior parte doAs bolachas no N3 para fluir em direção a N3P. "